Foundation Of VLSI Design L1

Other Details

Duration

Btech | Mtech Prer-final Year

Btech | Mtech Final Year

Passout Candidates

Mode of Delivery

Offline - Noida

Note:

- Because of Pandemic - We are operating in both mode right now (Offline & Online)

Trainers

Mr. Puneet Mittal

- He is Founder and CEO of VLSI Expert Pvt. Ltd. He is very much passionate about the teaching and mentoring to students. He has 14+ Semiconductor Industry experience. Know more about him

Other Industry Trainers

- Trainers from our associated company Like Technoready

- Industry Experts from Cadence & Synopsys as a Guest Invite

- Average Experience of 10+years in Semiconductor Industry

Fee Structure

Rs 55,000/- Only

Note:-

- Inclusive all Taxes

- Please don't ask for any discount. It's already at minimum price

- Payment can be done in 2 Instalments (60% & 40% ratio)

- Payment link can be share on request basis

Contact us

support@vlsiexpert.com

Upcoming batch

Foundation Of VLSI Design L1

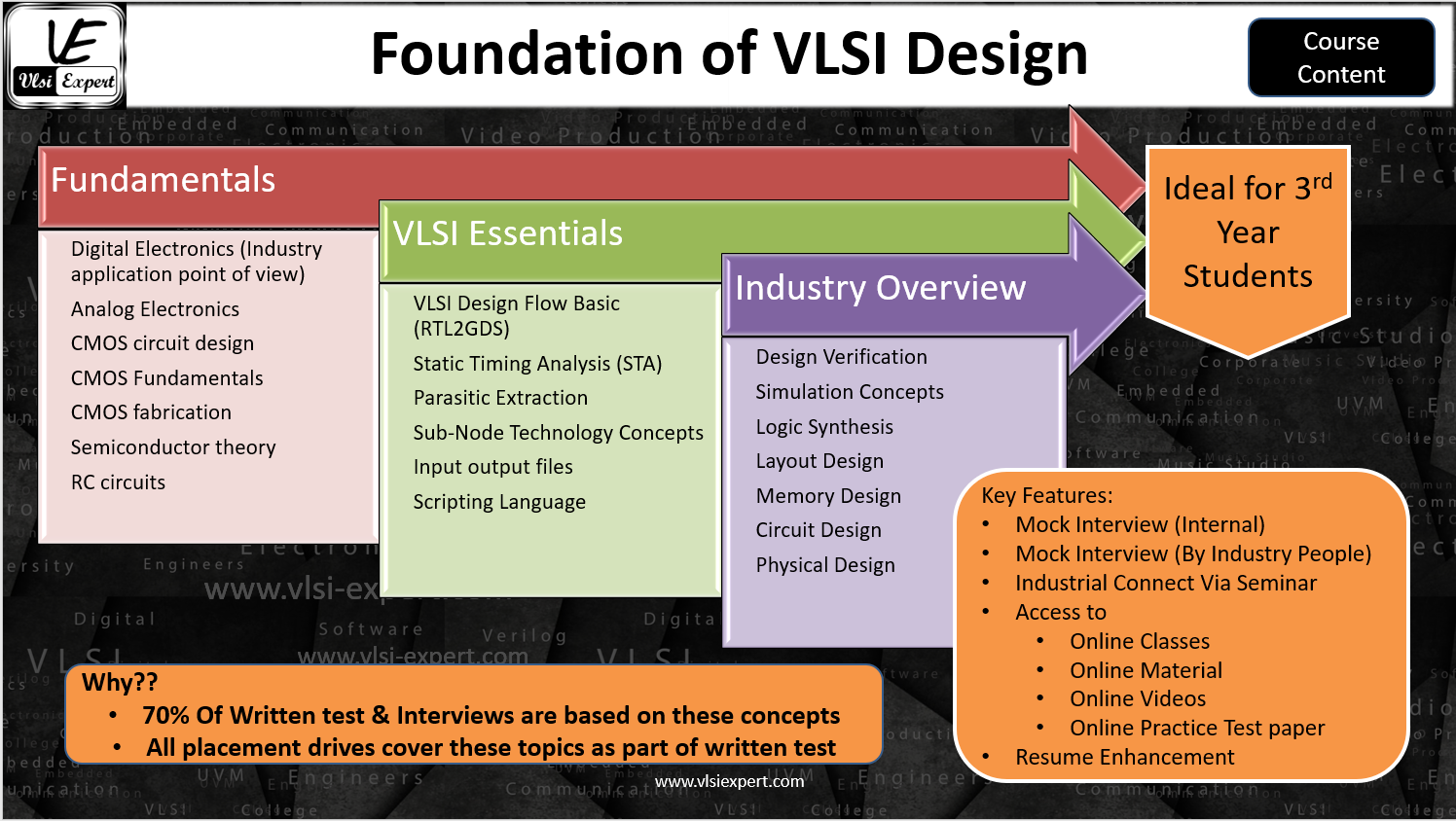

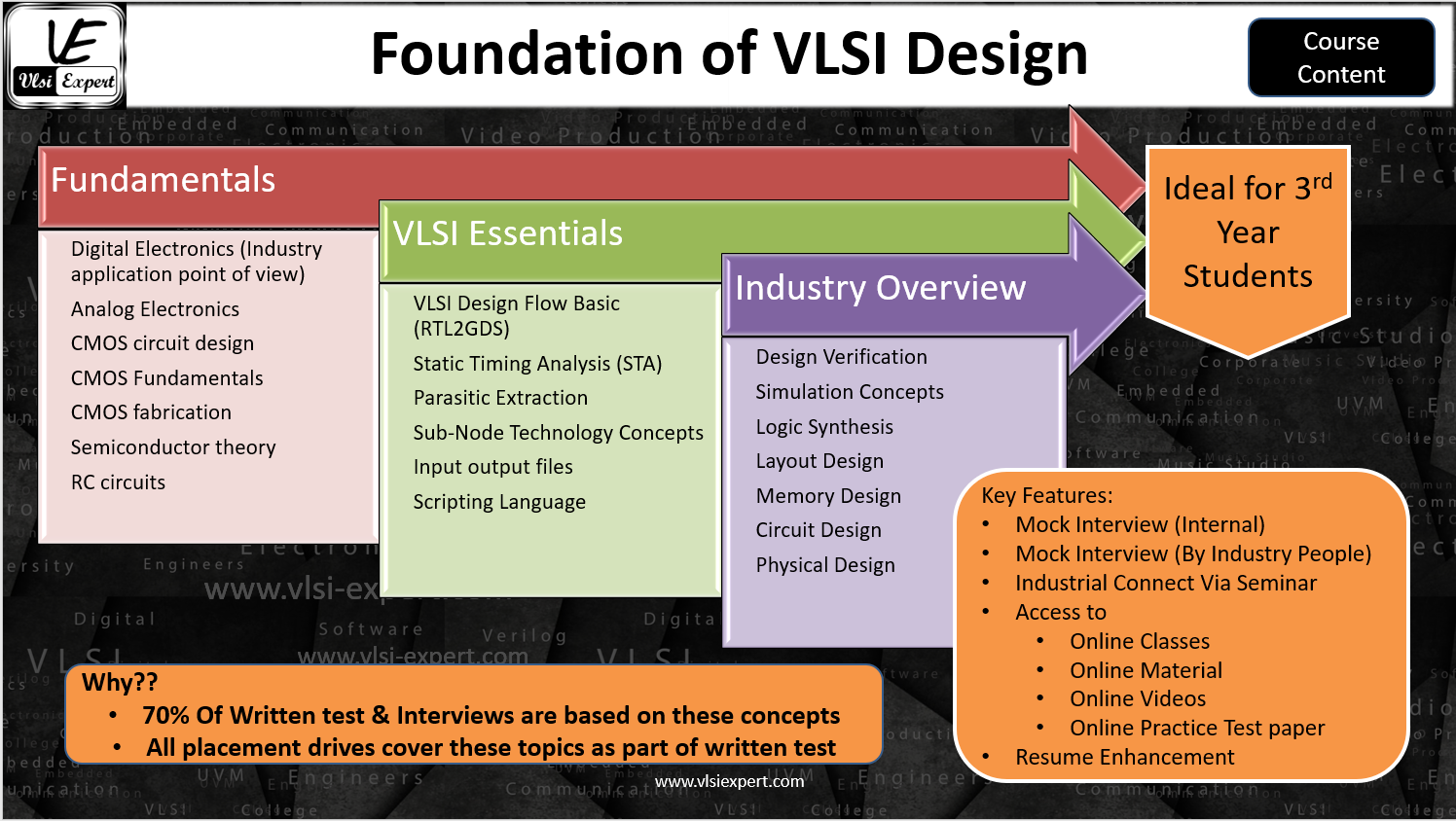

This course is specially designed for the Freshers. As name says it's a foundation course. Every Company first focuses on the fundamental of the engineering subjects.WRITE SHORT SUMMARY.

About the course

Highlight Of Course

Btech | Mtech Prer-final Year

Key Features

Offline - Noida

Associated Profiles in VLSI Industry

Why Should I join?

What will I achieve from this?

Contact Us

support@vlsiexpert.com

Upcoming batch

Student's Review

Madhuparna Das

We can't predict our future. But we can make choices & wish that things placed in the right place. One of my students Madhuparna Das also dreamed similar thing long back and we (#VLSI Expert Family member) all feel proud that she is now in Cadence Design Systems.

Like I always say- "Be Expert By Expert"

College: Accurate Institute of Management and Technology - Greater Noida

Year of Passing: 2018

Placement/year: Cadence /2018 (as Intern)

Current Status: In Cadence (Permanent)

Profile: STA Engineer

Geetika Singh

Understanding about #VLSI Industry & it's requirement before Training Vs after Training. One of my #student "Geetika Singh" placed in "Synopsys Inc" after successfully clearing 4-5 rounds. It's her #dream #company & I am happy that she cracked that. Her passion, efforts, hard-work & believe in herself are the only few reasons for her success.

#Fundamentals & #Basics are the foundation of every Industry but unfortunately, students are lacking big time in this area. As a VlsiExpert offline Training Program, I am focusing on this aspect. EDA tools can change, tool's command can change but tool's fundamental can't be changed. We are Engineers - "Tools should not command us - we should command Tools."

You should listen to this 2.5min Video & I can bet it will #motivate every fresher.

College: ABES Engineering College

Year of Passing: 2018

Placement/year: Synopsys /2018 (as Intern)

Current Status: In Synopsys (Permanent)

Profile: Standard Cell Layout Design

Rishu Shukla

https://www.linkedin.com/in/rishu-shukla-227631126/

College: ABES Engineer College

Year of Passing: 2018

Placement/year: Synopsys-Gatelength / 2019

Current Status: In Synopsys (Contractor)

Profile: Memory Layout Profile

When I look back on my journey of achieving what I want to be, I see the guidance, motivation and great support of my mentor Puneet Mittal sir which has led me finally to get into a VLSI industry. And a special thanks to Avnish Shukla sir for their help and support.When I was persuing b.tech I did not have an iota about VLSI and I never thought of getting into the core industry. Even when I get to know about VLSI then also I had doubts whether I will be able to achieve this or not. But one person who had a trust and belief on my capabilities was Puneet sir.

In VLSI EXPERT you don't just mug up the concepts and get a placement. You grow over here. Your personality, self belief, way of learning, attitude is developed over here. Just follow the instructions of Puneet sir and you will see a vast change in your learning and in all the other aspects.

In my case I had a doubt whether I will be able to achieve this or not one year back but he took out the best of me.He motivated me everytime whenever I felt low. Sir you are the reason I didn't give up. This journey is never be possible without you. Thank you for all your love and support.

Shriya Jain

https://www.linkedin.com/in/shriya-jain-503514145/

College: JP Engineering College - Noida

Year of Passing: 2019

Placement/year: Cadence / 2019 (As Intern)

Current Status: In Cadence (Intern)

Profile: STA Profile (Timing Team)

You have been a great mentor, teacher or guide.Thank you, sir, for encouraging me during my difficult times.I will always be grateful for the knowledge & skills that I gained from you.Thank you once again, sir

#God of STA

Shraddha Maheshwari

https://www.linkedin.com/in/shraddha-maheshwari-5365b3128/

College: ABES Engineering College

Year of Passing: 2019

Placement/year: Synopsys / 2019 (As Intern)

Current Status: In Synopsys (Intern)

Profile: Physical Design Engineer

Your continous support and faith in the person turns eveything possible. I have learnt a lot from you and your discussions with us. You don't only help us in developing skills but also shape our attitude towards learning and life. I don't understand how you manage your time to be available for us whenever we are in some trouble. It was all your belief in me and our conversations. The time when you said "mujh par vishwas hai ya nahi" was the point for my motivation. You even provided me a platform (as junior lab assisstant) to share what i have learnt with my mates which helped me to overcome my shortcomings. Thanks a lot sir for your motivation, time and constant support. Your mantra "you just need one opportunity" and "you are not going to lose anything but seekhne ko bht hai" will remain my motivation.

-Thank you sir 😇